# Energy modelling of multi-threaded, multi-core software for embedded systems

Steven P. Kerrison

A thesis submitted to the University of Bristol in accordance with the requirements of the degree Doctor of Philosophy in the Faculty of Engineering, Department of Computer Science, September 2015.

51,000 words.

Copyright © 2015 Steven P. Kerrison, some rights reserved.

This work is licensed under the Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License.

http://creativecommons.org/licenses/by-nc-nd/4.0/

## Abstract

Efforts to reduce energy consumption are being made across all disciplines. ICT's contribution to global energy consumption and by-products such as CO2 emissions continues to grow, making it an increasingly significant area in which improvements must be made. This thesis focuses on software as a means to reducing energy consumption. It presents methods for profiling and modelling a multi-threaded, multi-core embedded processor at the instruction set level, establishing links between the software and the energy consumed by the underlying hardware.

A framework is presented that profiles the energy consumption characteristics of a multi-threaded processor core, associating energy consumption with the instruction set and parallelism present in a multi-threaded program. This profiling data is used to build a model of the processor that allows instruction set simulations to be used to estimate the energy that programs will consume, with an average of 2.67 % error.

The profiling and modelling is then raised to the multi-core level, examining a channel based message passing system formed of a network of embedded multi-threaded processors. Additional profiling is presented that determines network communication costs as well as giving consideration towards system level properties such as power supply efficiency. Then, this is used to form a system level energy model that can estimate consumption using simulations of multi-core programs. The system level model combines multiple instances of a core energy model with a network level communication cost model.

The broader implications of this work are explored in the context of other embedded and multi-core processor architectures, identifying opportunities for expanding or transferring the models. The models in this thesis are formed at the instruction set level, but have been demonstrated to be effective at higher-levels of abstraction than instruction set simulation, through their support of further work carried out externally.

This work is enabled by several pieces of development effort, including a profiling framework for taking power measurements of the devices under investigation, tools for programming, routing and debugging software on a multi-core hardware platform called Swallow, and enhancements to an instruction set simulator for the simulation of this multi-core system.

Through the work of this thesis, an embedded software developer for multi-threaded and multi-core systems is equipped with tools, techniques and new understanding that can help them in determining how their software consumes energy. This raises the status of energy efficiency in the software development cycle as we continue our efforts to minimise the energy impact of the world's embedded devices.

#### Acknowledgements

I owe the successful completion of this PhD thesis to a great many people, and I can directly thank but a few of them here. If I interacted with you during the course of my research, please know that I am eternally grateful for that. Thank you to my family for supporting and encouraging me throughout.

Thank you to my supervisor, Kerstin Eder, whose guidance helped me develop a compelling research topic and secure funding for my work, without which none of this would have been possible. Thank you to Simon Hollis and Jake Longo Galea for creating a rather interesting set of research problems for us to collectively solve in the Swallow platform. David May, your thought provoking discussions have been invaluable and inspiring. Many thanks to my external examiners, Alex Yakovlev and Peter Marwedel, as well as my internal coordinator José Luis Núñez-Yáñez.

My colleagues and companions in research deserve much gratitude for their input, collaboration, and of course their tolerance. Jamie Hanlon, Roger Owens, Neville Grech, Kyriakos Georgiou, Jeremy Morse and James Pallister, you and many others in the department made research an exciting experience. A special thank you to Dejanira Araiza Illan for your support, particularly during the write-up.

In the first year of my studies I was hosted by XMOS. This was an excellent place to form ideas, gain industrial insight and motivate my work. In particular, thanks to Henk Muller, John Ferguson, Matt Fyles and Richard Osborne for their expert advice and support.

My work was funded by a University of Bristol PhD Scholarship, and much of it became relevant to the ENTRA EU FP7 FET research project. I am grateful to these funding sources for making this work possible, and for creating an ecosystem in which to disseminate and further explore this work.

## Author's declaration

I declare that the work in this dissertation was carried out in accordance with the requirements of the University's Regulations and Code of Practice for Research Degree Programmes and that it has not been submitted for any other academic award. Except where indicated by specific reference in the text, the work is the candidate's own work. Work done in collaboration with, or with the assistance of, others, is indicated as such. Any views expressed in the dissertation are those of the author.

Signed:

Date:

# Contents

| Lis | ist of Figures                                                                                                                                                                                                                                                                             | 13                                      |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Lis | ist of Tables                                                                                                                                                                                                                                                                              | 15                                      |

| Lis | ist of Code Listings                                                                                                                                                                                                                                                                       | 15                                      |

| 1.  | Introduction         1.1. Research questions and thesis         1.2. Contributions         1.3. Structure         1.4. Terminology and conventions                                                                                                                                         | <b>17</b><br>18<br>20<br>22<br>23       |

| ۱.  | Background                                                                                                                                                                                                                                                                                 | 25                                      |

| 2.  | <ul> <li>Parallelism and concurrency in programs and processors</li> <li>2.1. Concurrent programs and tasks</li> <li>2.2. Parallelism in a single core</li> <li>2.3. Multi-core processing</li> <li>2.4. Summarising parallelism and concurrency</li> </ul>                                | <b>29</b><br>33<br>35<br>36             |

| 3.  | <ul> <li>Energy modelling</li> <li>3.1. Hardware energy modelling</li> <li>3.2. Software energy modelling</li> <li>3.3. Summary</li> </ul>                                                                                                                                                 | <b>39</b><br>40<br>42<br>44             |

| 4.  | <ul> <li>Influencing software energy consumption in embedded systems</li> <li>4.1. Forming objectives to save energy in software</li></ul>                                                                                                                                                 | <b>47</b><br>47<br>50<br>54<br>56<br>56 |

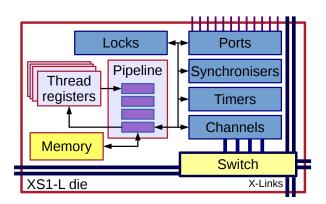

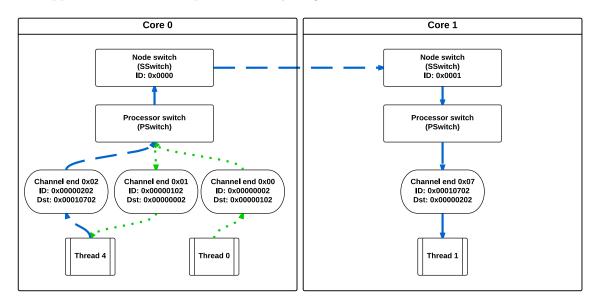

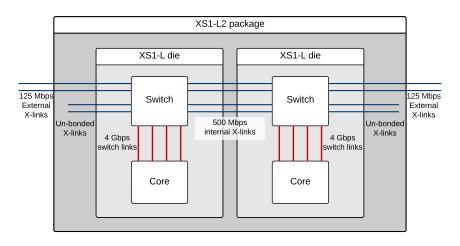

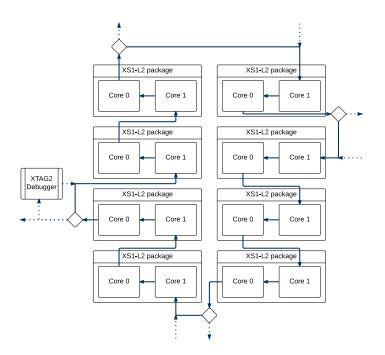

|     | <ul> <li>A multi-threaded, multi-core embedded system</li> <li>5.1. The XS1-L processor family</li></ul>                                                                                                                                                                                   | <b>59</b><br>59<br>65<br>71             |

| 11. | . Constructing a multi-threaded, multi-core energy model                                                                                                                                                                                                                                   | 73                                      |

| 6.  | Model design and profiling of an XS1-L multi-threaded core         6.1. Strategy         6.2. Profiling device behaviour         6.3. Model design considerations         6.4. XMProfile: A framework for profiling the XS1-L         6.5. Generating tests         6.6. Profiling summary | 77<br>77<br>79<br>80<br>83<br>85        |

| 7.  | Core level XS1-L model implementation                                    | 87           |

|-----|--------------------------------------------------------------------------|--------------|

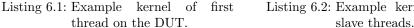

|     | 7.1. Workflow                                                            | 87           |

|     | 7.2. A preliminary model                                                 | 88<br>97     |

|     | 7.4. An extended core energy model                                       | 97<br>100    |

|     | 7.5. Evaluation of the extended model                                    | 100          |

|     | 7.6. Beyond simulation                                                   | 107          |

|     | 7.7. Summary                                                             | 109          |

| 8.  | Multi-core energy profiling and model design using Swallow               | 111          |

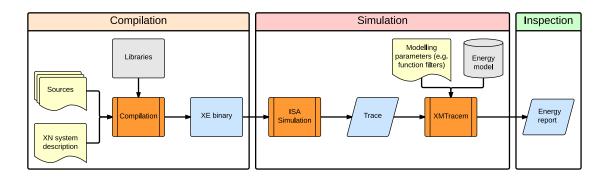

|     | 8.1. Core energy consumption on Swallow                                  | 111          |

|     | 8.2. Network communication energy profiling                              | 113          |

|     | 8.3. Determining communication costs                                     | 115          |

|     | 8.4. Summary of Swallow profiling                                        | 117          |

| 9.  | Implementing and testing a multi-core energy model                       | 119          |

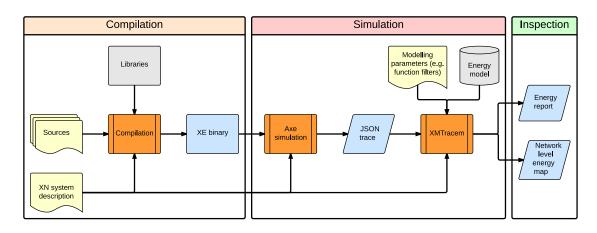

|     | 9.1. Workflow                                                            | 119          |

|     | 9.2. Core and network timing simulation in axe                           | 120          |

|     | 9.3. Communication aware modelling                                       | 122          |

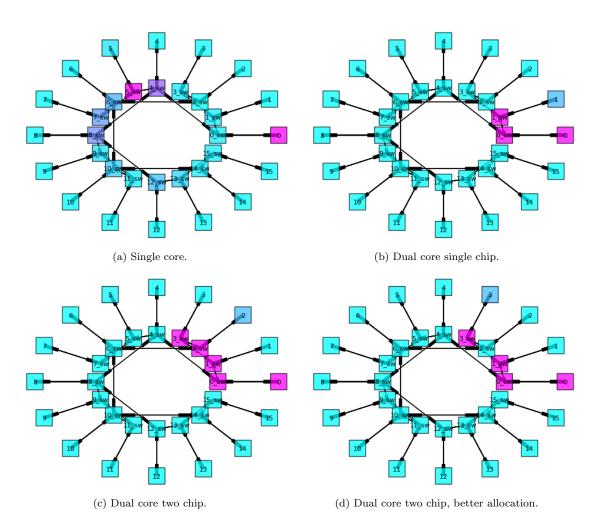

|     | 9.4. Displaying multi-core energy consumption data                       | 126          |

|     | 9.5. Demonstration and evaluation       9.5                              | 128          |

|     | 9.6. 1/O as an adaptation of the network model                           | $132 \\ 133$ |

| 10  |                                                                          | 135          |

| 10  | Beyond the XS1 architecture                                              | 135          |

|     | 10.1. Epipinary                                                          | $135 \\ 137$ |

|     | 10.3. Multi-core ARM implementations                                     | 139          |

|     | 10.4. EZChip Tile processors                                             | 140          |

|     | 10.5. Summary of model transferability                                   | 141          |

| 11  | Conclusions                                                              | 143          |

|     | 11.1. Review of thesis contributions                                     | 143          |

|     | 11.2. Building a multi-core platform for energy modelling research       | 144          |

|     | 11.3. ISA-level energy modelling for a multi-threaded embedded processor | 144          |

|     | 11.4. Multi core software energy modelling from a network perspective    | 145          |

|     | 11.5. The transferability of multi-threaded, multi-core models           | 146          |

|     | 11.6. Writing energy efficient multi-threaded embedded software          | 147          |

|     | 11.7. Future work                                                        | 148          |

|     | 11.8. Concluding remarks                                                 | 149          |

| Lis | t of acronyms                                                            | 151          |

| Bil | bliography                                                               | 155          |

# List of Figures

| 2.1. 2.2.                                                                                      | 11                                                                                                                                                                                                                                                  | $\frac{31}{34}$                                          |

|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 4.1.<br>4.2.                                                                                   | 0 0                                                                                                                                                                                                                                                 | $54 \\ 55$                                               |

| $5.1. \\ 5.2. \\ 5.3. \\ 5.4. \\ 5.5. \\ 5.6.$                                                 | Channel communication in the XS1 ISA                                                                                                                                                                                                                | 60<br>63<br>65<br>66<br>68<br>69                         |

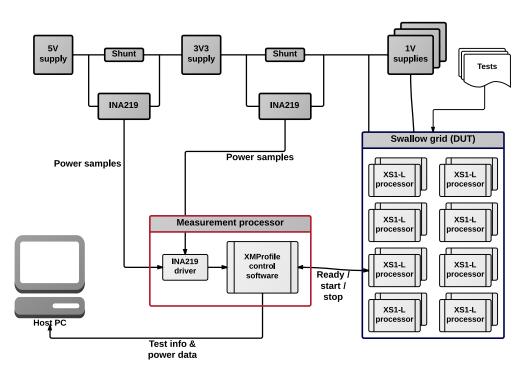

| 6.1.<br>6.2.<br>6.3.                                                                           | XMProfile test harness hardware and software structure                                                                                                                                                                                              | 78<br>81<br>82                                           |

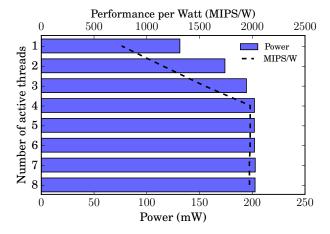

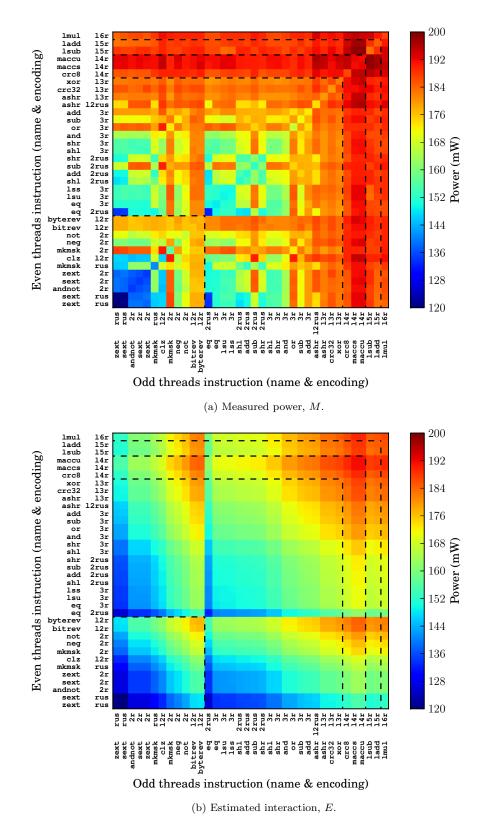

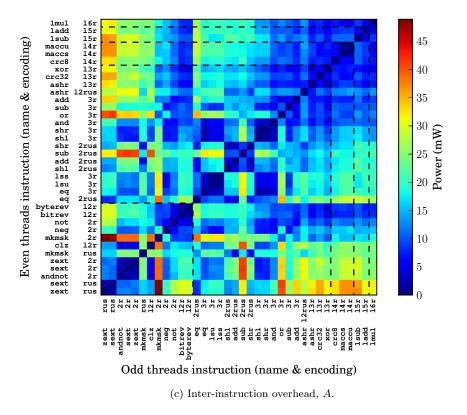

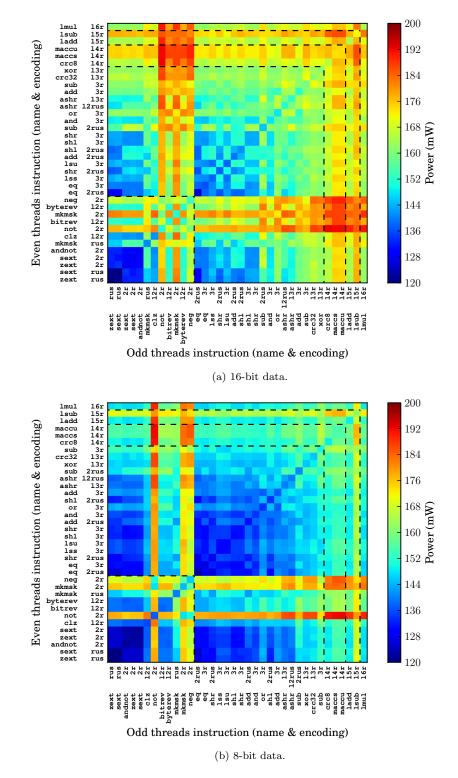

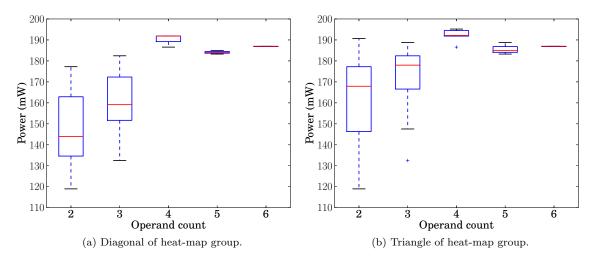

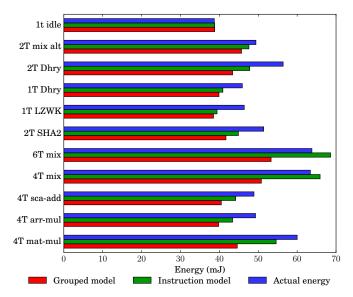

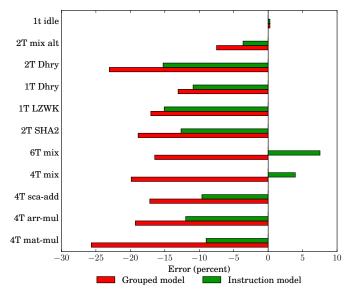

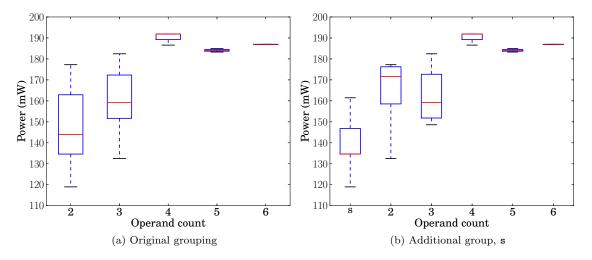

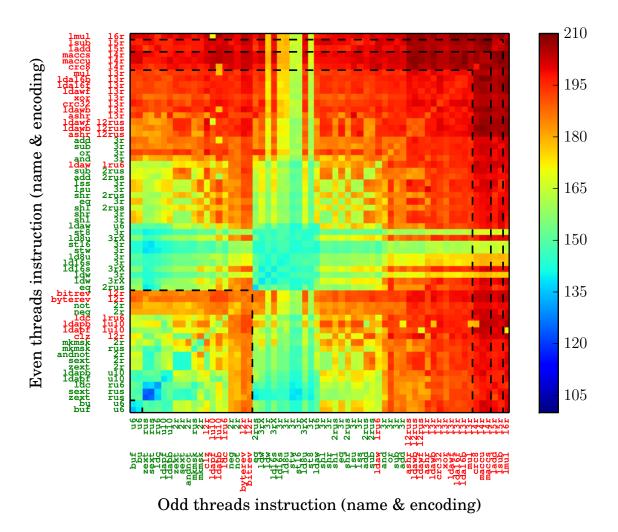

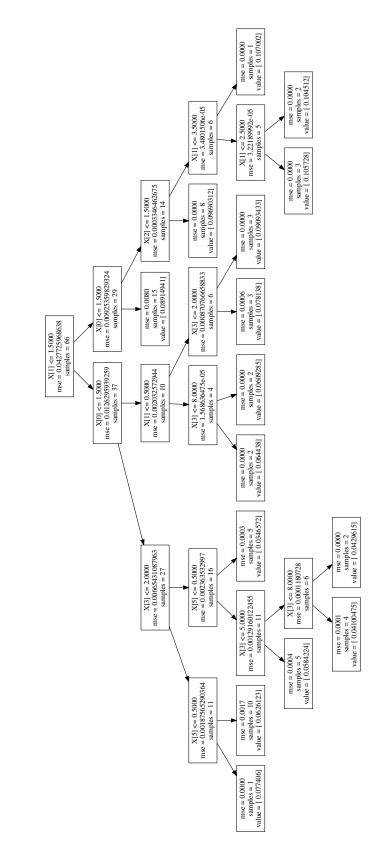

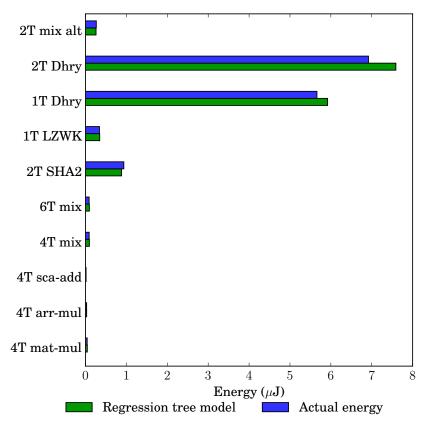

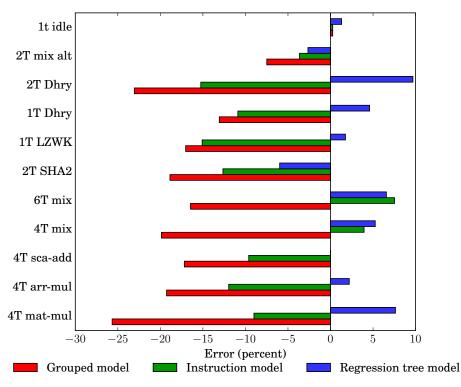

|                                                                                                | Active and inactive thread costs for the XS1-L processor                                                                                                                                                                                            | 87<br>89<br>91<br>93<br>95<br>99<br>00<br>02<br>05<br>08 |

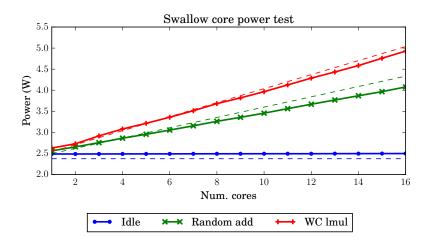

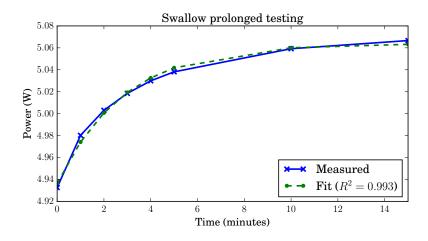

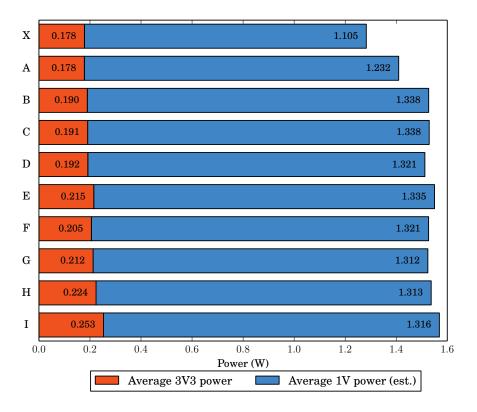

| <ol> <li>8.1.</li> <li>8.2.</li> <li>8.3.</li> <li>8.4.</li> </ol>                             | Heat sensitivity of Swallow profiling                                                                                                                                                                                                               | 13<br>13<br>14<br>16                                     |

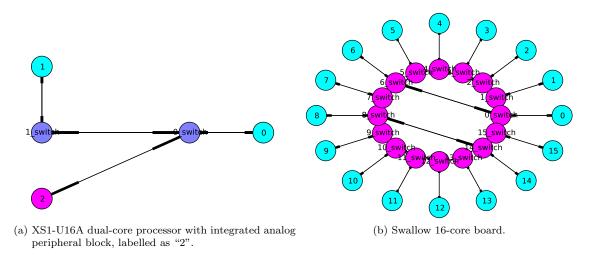

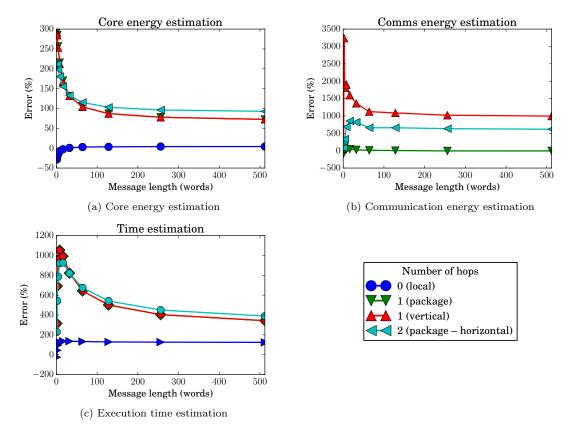

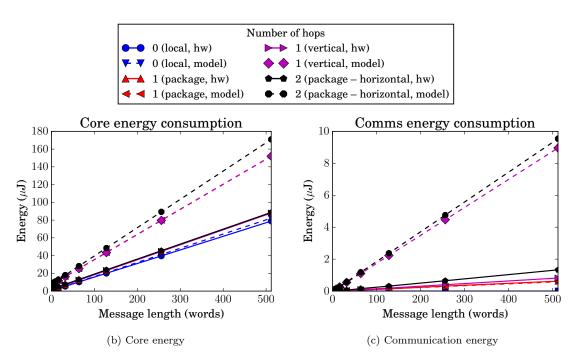

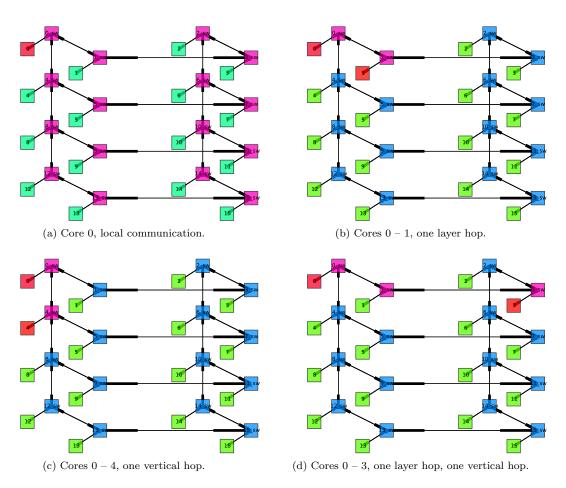

| <ol> <li>9.1.</li> <li>9.2.</li> <li>9.3.</li> <li>9.4.</li> <li>9.5.</li> <li>9.6.</li> </ol> | Top-level abstraction of components in a modelled multi-core network       1         Network-level energy consumption visualisation       1         Multi-core modelling accuracy       1         Measured and estimated energy consumption       1 | 19<br>24<br>28<br>31<br>31<br>32                         |

# List of Tables

| 2.1.                                                               | Example of a five stage processor pipeline, including warm-up and stalling 3                                                                                                          | 33         |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.1.                                                               | Energy modelling technique overview                                                                                                                                                   | <b>8</b> 9 |

|                                                                    | 6 I                                                                                                                                                                                   | 70<br>71   |

| 6.1.<br>6.2.                                                       | 1 0                                                                                                                                                                                   | 80<br>83   |

| <ol> <li>7.2.</li> <li>7.3.</li> <li>7.4.</li> <li>7.5.</li> </ol> | Hamming weight of inputs and outputs for interleaved lmul instructions9Power measurements for lmul under differing data conditions9Benchmarks used to evaluate energy model accuracy9 |            |

| 8.1.<br>8.2.<br>8.3.                                               | Calibration tests for Swallow       11         Test combinations for communication power measurements       11         Swallow communication cost validation       11                 | 5          |

| 9.1.<br>9.2.<br>9.3.                                               | Definition of elements in axe JSON trace12Graph attributes for multi-core model12Resource instructions for network communication12                                                    | 23         |

| 10.1                                                               | Architecture comparison summary 14                                                                                                                                                    | 1          |

# List of Code Listings

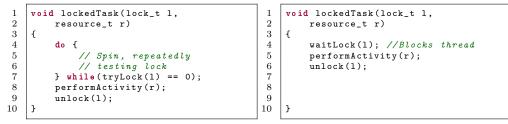

|      | Spinlock loop    56      Event-driven wait    56                                                   |

|------|----------------------------------------------------------------------------------------------------|

|      | Sending on a channel    63      Receiving on a channel    63                                       |

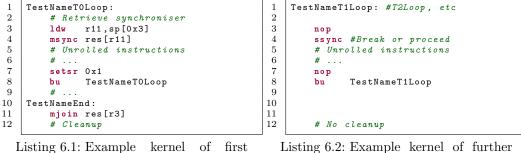

|      | Example kernel of first thread on the device under test82Example kernel of further slave threads82 |

| 8.1. | XC top-level multi-core allocation example                                                         |

|      | Example JSON trace line from <b>axe</b>                                                            |

## 1. Introduction

The goal of saving energy is considered a contemporary challenge, motivated by several factors, but dominated by two: managing the world's consumption of resources and limiting the rate at which we produce harmful by-products of that consumption, such as carbon dioxide. In computing, however, it is not necessarily a contemporary challenge, nor do those two factors alone form the primary goals.

Energy has always governed the uses for and effectiveness of computers. Mechanical computers were large and slow, whilst the adoption of vacuum tubes offered higher performance. The transistor and its subsequent miniaturisation to nanometer scale allowed computers to increase in speed, reduce in size, and consume a small enough amount of energy to be pervasive devices in offices, homes and vehicles.

While the practicalities of energy consumption in computing have been a governing factor for nearly a century, the motivation to reduce processor energy continues, as the Internet of Things (IoT) — an ever-growing number of interconnected embedded devices — creeps into the technological lexicon. These devices must be small and consume tiny amounts of energy, often powered by minute batteries or via energy harvesting.

Using energy consumption data from studies into data centers, PCs, network hardware and other Information and Communication Technology (ICT) equipment, ICTs energy consumption was determined to be 8% of global consumption in 2008 [Pic+08]. Therefore, progress towards both environmental and product-centric goals can be made by continuing to reduce the energy consumption of devices.

As we reach technological limits, new techniques must be created to allow progress. For decades we have relied, and continue to rely upon Moore's Law [Moo65] and trends related to it. The shrinking of transistors and improvements in process technology yield energy efficiency improvements, but now more aggressive energy saving techniques are devised and applied at higher levels, from circuitry to turn off temporarily unused silicon, up to software controlled sleep states. The advent of multi-core, which was necessary to avoid the practical limits of operating frequency and power, introduces new opportunities but also new challenges, particularly in the areas of task scheduling and effective programming models.

As the aggressiveness of energy saving techniques increases, the software that runs on top of the processor eventually becomes a point of interest. This software is ultimately responsible for the behaviour of the hardware — the hardware exists to perform the tasks defined in software by the authors of that software. The software, therefore, is largely responsible for a device's energy consumption. To re-state the argument from a bottom-up perspective, a device with many energysaving features is inefficient if the software running on it prevents those features from being used, or fails to adequately exploit them.

An abundance of evidence towards this is present in mobile phones, where devices must be designed to be energy efficient. However, a large number of software energy bugs have been observed at all levels of the software stack [PHZ11]. These software problems amount to 35 % of the energy bugs surveyed. Typically, these bugs prevent the hardware from entering low power states. Energy bugs have several negative impacts, including poor reviews for buggy applications, reports of phones with poor battery life and even increased product returns.

In order to write energy efficient software, developers must understand the energy that their code will consume. To that end, this thesis proposes new techniques for addressing the imbalance between understanding of hardware energy consumption and how the software running upon that hardware affects it.

The focus of this work is on multi-threaded and multi-core processors in the embedded system space, where the processor contributes a significant proportion of system energy consumption. This is evident if we consider a particular device class: the mobile phone. The most significant energy consumption within these devices is a combination of back-light, display, radio, graphics and processor [CH10]. If we consider that in a more deeply embedded system, such as one not interacting directly with humans, then the display, along with back-light and graphics processor, are no longer present. Thus, the processor's energy consumption becomes dominant. Further, in such systems, energy is often in scarce supply, either due to the delivery mechanism or storage method, for example a battery of limited capacity. It is desirable to maximize energy efficiency in order to reduce the complexity of providing sufficient energy to these devices. The goal of this work is to propose new methods for identifying how software consumes energy in such systems, supporting these proposals with experimental tools, energy models, along with testing and evaluation. These contributions can then be used as the basis for future work.

The research herein includes an in-depth study of a multi-threaded processor, assembled into multi-cores. The hardware's energy consumption, and its relationship to the software running upon it, is analysed at multiple levels, starting at the instruction set and progressing to a system level considering multiple networked cores. Through this analysis, this thesis is able to present an energy model for a multi-threaded embedded processor architecture and raise that modelling up to the multi-core level. It is shown that a combination of understanding the target hardware and writing software that fits the hardware well is essential for energy efficiency.

Software is selected to demonstrate behaviours typical of an embedded system, including multithreaded and multi-core examples. This software is compiled and the executables are then energy modelled using simulation at the instruction set level. The presented core-level multi-threaded energy model delivers accuracy within 10% of measured hardware energy consumption and 2.67% on average, with a standard deviation of 4.40 percentage points. At the network level, absolute energy estimations diverge from the hardware. However, the energy implications of communicating tasks are made clear through the reporting and visualisation methods that are presented. Most importantly, the relative improvements (or otherwise) from changes to the software can be observed without the detailed hardware modelling used in processor design, and without needing to instrument the target hardware. This makes energy modelling more accessible to the software developer.

Finally, this work enables higher level analyses, such as static analysis, to be performed, by feeding the model data into them. Thus, this research aims to provide enlightenment to software engineers with an interest in the energy consumption of their embedded software, and to other researchers seeking new methods to provide and act upon this information through reporting and optimisation.

The rest of this introductory chapter formally defines the research questions posed in this work, summarises the contributions of this thesis along with related publications, outlines the structure of the document and states the terminology and conventions used within.

## 1.1. Research questions and thesis

At its core, this thesis seeks to further the state of the art in energy modelling of software. It does so by focusing at the embedded device level, observing emerging changes in how devices are constructed and used across ICT. The fundamental question that lies beneath this work can be posed from the perspective of an embedded systems software developer:

### How much energy will the software that I am writing consume?

Without sufficient hardware knowledge, there is very little intuition when seeking the answer to this question. Yet, in embedded systems, energy consumption is critical to the safe and correct operation of a device. If this question can be answered, then the software developer can make educated decisions about what action to take, be it make changes to their software, modify the system hardware, or re-visit the specification.

This question is quite a broad one, which when asked by an embedded software developer, indicates a specific goal: to minimise energy consumption in order to provide optimal functionality of the embedded device, without breaking any of the constraints essential to its correct operation. This can be phrased as a more specific question:

# Software that is a good fit to the underlying hardware is more energy efficient, but how can I achieve this?

Whilst abstraction allows a developer to avoid concerning themselves with the engineering beneath the level at which they want to work, understanding how higher-level implementations map down to low-level activity is fundamentally important, both in terms of performance and energy. Regardless of energy saving features in the hardware, a piece of software that neither directly exploits the best features of the hardware, nor passively allows the features to work, will lead to sub-optimal power [RJ97]. This is true historically and continues to be true today, and methods for allowing this mapping to take place must continue to be developed if energy consumption of software is to be better understood on contemporary hardware. Understanding this research question also provides insight into what software is not a good fit to a particular system.

This thesis contributes new answers to these research questions. The statements underpinning the work of this thesis are as follows:

**Effective energy estimates for modern embedded software must consider multi-threaded, multicore systems.** Parallelism in hardware is now necessary as a means to deliver increases in performance. This requires multi-threading and multi-core hardware, and by extension software that maps onto this type of system.

**Energy modelling at the instruction set level provides good insight into the physical behaviour of a system whilst preserving sufficient information about the software.** To be useful to a software developer, an energy model must be expressible in a way that relates to both the software and the underlying hardware, exposing reasons for the behaviours that are seen.

**Energy saving and energy modelling techniques are placed under greater constraints in the embedded space.** In an embedded system with hard real-time constraints, software or hardware changes that may save energy cannot risk breaking those constraints. Similarly, the available hardware resources, such as performance counters, may make it difficult to collect data to aid energy modelling, either online or offline. This necessitates a modelling strategy that accounts for these limitations or is unaffected by them.

**Multi-threaded and multi-core devices introduce new characteristics that must be considered in energy models.** Embedded processors often have simpler pipelines than more general purpose counterparts, but the introduction of multi-threading and multi-core systems into the embedded space creates characteristics to consider. These characteristics can be unique to embedded systems, which address the need for more performance in different ways to larger processors, to enable them to satisfy the constraints placed on real-time systems. Further, the objective in such systems is to satisfy an energy budget that is often defined by a limited source of energy, such as a battery. This is in contrast to a high performance processor, which is more limited by heat dissipation and power delivery.

**Energy models that do not rely on run-time data from the processor provide greater flexibility for multi-level analysis.** Prior research has shown a variety of methods for estimating the energy consumption of software, some of which utilise real-time data from the processor. Such methods preclude higher level analysis, whereas this thesis presents methods that can be used across several levels of abstraction, from instruction set simulation up to abstract network level views.

Both absolute accuracy and relative indicators provide useful information to a developer. Where energy consumption constraints can be specified and are hard targets, an energy model must provide sufficient accuracy to give the developer confidence that they have or have not met that target. Using the performance of a range of prior research as a baseline, this accuracy threshold will be established as  $\pm 10\%$ . Without this confidence, the development cycle is lengthened

by the need to repeatedly deploy and test on real hardware, which may be significantly more inconvenient then running a simulation or other analysis. However, where an energy target is not absolute, or a higher level view and understanding are required, relative measures remain appropriate, for example to answer the question "which version of this software uses less energy?" Given the current lack of intuition towards software's contribution to energy consumption, this is still a valuable contribution to a developer's knowledge. What is important in such cases, however, is that a sufficiently wide view of the system is given, so that an apparent improvement in one area is not eclipsed by a side-effect created in another.

**Movement of data costs energy, no matter the form that movement takes.** The embedded processors studied in this work do not feature caches, nor do they use shared memory to communicate between threads. Thus, the significant energy consumption arising from cache misses and the memory hierarchy is not present. However, data must still be moved between threads via other means, and a synchronisation or other flow coordination effort between threads must take place. The cost of this must still be analysed and presented to the developer, in order to assist them in reducing energy. A network-level view of communicating threads presents a different paradigm for identifying how communication takes place and how improvements can be made, departing from the often complex behaviours of large memory hierarchies that can be difficult to reason about.

**Energy models for different architectures can have elements in common.** Parallelism is being provided in modern processor architecture in various ways, as challenges such as distributing data across or sharing data between cores seek to be addressed. Although this creates variety in how different processors behave and need to be programmed, an instruction set level energy model can include at least some transferable properties between different architectures. This serves to ensure the energy models can be developed for new architectures more rapidly.

From these statements, many questions can be raised that guide the research. The structure of this document follows these thesis statements closely, posing and investigating these questions progressively. An explanation of this document's structure is given in § 1.3.

## 1.2. Contributions

This thesis makes contributions to research in the areas of energy modelling of software, computer architecture and embedded systems. The main contributions and related publications are outlined in this section.

### Energy modelling a novel embedded processor architecture

The XMOS XS1 processor architecture has a number of novel aspects to it, relating to softwaredefined real-time Input/Output (I/O), hardware thread scheduling, parallelism in embedded processors and multi-core networks of message-passing processors. This thesis furthers the understanding of these architectural features in relation to energy consumption at the software level, defining the particular influences that software has upon this hardware.

## Contributing to the creation of a multi-core research platform

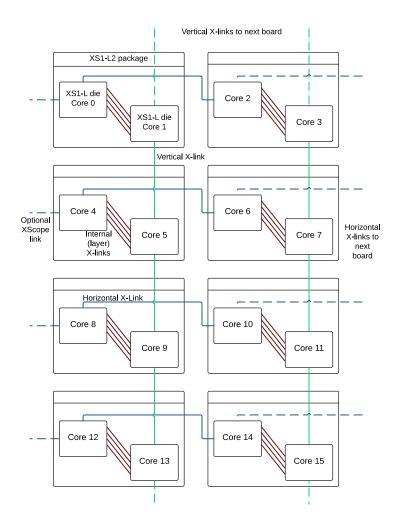

The Swallow project [Hol12] was created by Simon Hollis at the University of Bristol with the intention of building a real multi-core embedded system for demonstration and experimentation, where previously a significant amount of research was based purely upon modelled or theoretical systems. The Swallow platform forms an essential part of the research conducted in this thesis, specifically in studying and modelling multi-core communication costs.

The research conducted in this thesis has resulted in a number of significant contributions to the Swallow project, namely:

• Initial bring-up and testing of the Swallow hardware, post-manufacture.

- The introduction of wrapper scripts and pre-processing for the XMOS compiler tool-chain to provide support for the large number of processors, not previously handled by the compiler.

- Development and testing of the platform description files (XN files [XMO13a]), including mapping Joint Test Action Group (JTAG) device IDs to XMOS network node IDs and implementation of the deadlock-free dimension-order routing algorithm on Swallow's unique topology.

- Code to boot Swallow devices over their network links rather than JTAG, significantly reducing start-up time for large grids from over a minute to less than ten seconds.

- An Ethernet software stack to allow both Ethernet based Trivial File Transfer Protocol (TFTP) booting and communication with running applications.

- Communication libraries to provide more flexible channel communication than what is built into the XC language.

- A significant amount of hardware surgery involving a soldering iron, microscope and scalpel.

These contributes enabled the multi-core energy data that is presented in this thesis to be collected, and has assisted in the enablement of research by others using Swallow.

## Energy modelling of a network of embedded processors

This thesis traverses various levels of system abstraction, from Instruction Set Architecture (ISA) up to system level. At the system level, a Multi-Threaded and Multi-Core (MTMC) is viewed as a network of interconnected components. These components can be independently energy modelled, as well as the interconnects between them.

The core level energy model is combined with this relatively abstract network level view and a multi-core simulation, to provide energy modelling of embedded software with a unique level of detail given to *where* the most significant quantities of energy are consumed. This serves to provide better information into how software consumes energy in modern embedded systems, so that *informed* decisions can be made to reduce that energy consumption, rather than through undirected experimentation.

#### **Related publications**

The following publications are, at the time of writing, work directly related to this thesis. For each publication, a brief description of the relationship to the thesis is given.

• Steve Kerrison and Kerstin Eder. "Energy modelling of software for a hardware multithreaded embedded microprocessor". In: *Transactions on Embedded Computer Systems* (*TECS*) (2015) [KE15b]

This journal paper describes the initial energy profiling phase and preliminary model that was produced for a sub-set of the XMOS XS1 ISA. This thesis contains that same work, described in more detail, and then built upon to produce a refined model for full ISA.

Umer Liqat, Steven Kerrison, Serrano Alejandro, Kyriakos Giorgiou, Pedro Lopez-Garcia, Neville Grech, Manuel V. Hermenegildo, and Kerstin Eder. "Energy Consumption Analysis of Programs based on XMOS ISA-Level Models". In: 23rd International Symposium on Logic-Based Program Synthesis and Transformation (LOPSTR'13). Springer, Sept. 2015 [Liq+15]

The model described in [KE15b] is used in this paper as the basis for providing energy consumption predictions through static analysis of the software. The author of this thesis contributed a description of the model to the paper, along with simulation based energy estimation results, for comparison with the static analysis method.

• Steve Kerrison and Kerstin Eder. "Measuring and modelling the energy consumption of multi-threaded, multi-core embedded software". In: *ICT Energy Letters* (July 2014), pp. 18–

19. URL: http://www.nanoenergyletters.com/files/nel/ICT-Energy\_Letters\_8.

pdf [KE14]

This letter summarises work on further development of the model in [KE15b], along with preliminary results into the impact of multi-processor communication costs. The Swallow project, which is also described in this thesis, is an essential part of this work.

• Steve Kerrison and Kerstin Eder. "A software controlled voltage tuning system using multipurpose ring oscillators". In: *arXiv* (2015). arXiv: 1503.05733. URL: https://arxiv. org/abs/1503.05733 [KE15a]

The ring oscillators onboard the XMOS XS1-L are used in this work to calibrate an optimised safe (faultless) core voltage for a given operating frequency. Components of this work, particularly the background, are used in § 4.2.3.

Simon J. Hollis and Steve Kerrison. "Overview of Swallow — A Scalable 480-core System for Investigating the Performance and Energy Efficiency of Many-core Applications and Operating Systems". In: arXiv (2015) [HK15]

This overview of the Swallow system describes the salient parts of its construction, such as the routing, performance, and energy consumption. This thesis and the work surrounding it has contributed to the figures and information presented in the paper.

Neville Grech, Kyriakos Georgiou, James Pallister, Steve Kerrison, Jeremy Morse, and Kerstin Eder. "Static analysis of energy consumption for LLVM IR programs". In: Proceedings of the 18th International Workshop on Software and Compilers for Embedded Systems. SCOPES '15. Sankt Goar, Germany: ACM, 2015. DOI: 10.1145/2764967.2764974 [Gre+15]

The energy models from this thesis and [KE15b] are leveraged in this paper to perform static analysis at the LLVM IR level — the intermediate representation used in the LLVM compiler toolchain. This provides potentially richer program information than at the ISA level, preserving more control flow and other data, assisting the analysis process. For the XMOS XS1 model, this work was enabled by a mapping between the instructions used in the ISA level model and sequences of LLVM IR instructions. The author of this thesis contributed the XMOS ISA model data, as well as hardware and simulation based energy results. The static analysis and mappings between LLVM IR and ISA were contributed by the other authors of the paper.

## 1.3. Structure

This document is structured to follow the arguments that form the thesis described in § 1.1. Each of the thesis statements builds upon the research conducted in response to the points before it. To effectively communicate this research this work is divided into two main parts, each comprising several chapters.

Part I addresses prior work and essential background. Parallelism is explored in Chapter 2, drawing attention to the topic from both a software and hardware perspective. A variety of energy modelling methods are then detailed in Chapter 3, including discussion of the challenges that parallelism introduces to the energy modelling process.

Chapter 4 then draws upon the previous two chapters to address the properties of modern embedded systems that present further challenges to energy modelling of software. Part I is concluded with Chapter 5, which examines the XMOS XS1-L processor core and a system of these processors assembled into a grid style network; the Swallow project. The unique properties of the processor and Swallow are discussed, in relation to the topics presented in the previous chapters. This lays out the key challenges that guide the implementation decisions of this thesis.

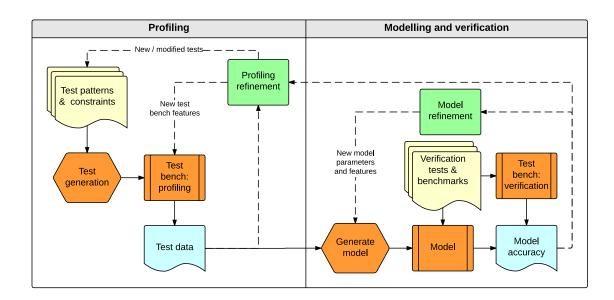

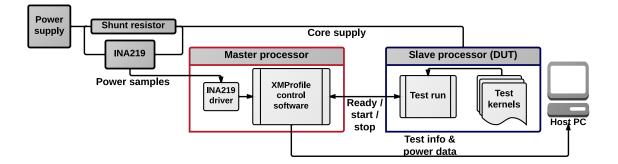

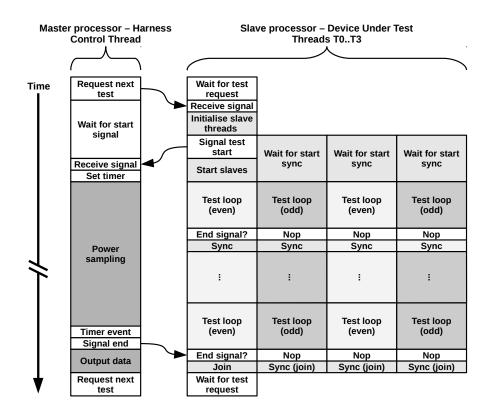

Part II focuses on implementation, using the previously established background work, combined with new research, to address the statements made in § 1.1. It begins with two chapters that focus on a single XS1-L multi-threaded processor core. Chapter 6 presents methods for relating the energy consumption of the XS1-L to its ISA, through a newly developed profiling rig, comprising both hardware and software. The profiling demonstrates a number of the properties of energy consumption that are unique to this particular multi-threaded embedded processor. Chapter 7 then uses this profiling data to construct an ISA level model that can be used at various levels of abstraction, starting with instruction set simulation. Several variations of the model are presented and evaluated in order to determine the best possible model accuracy.

The subsequent two chapters are structured in a similar fashion, presenting the profiling techniques and simulation tools used for the multi-core Swallow system in Chapter 8, then the model and evaluation in Chapter 9. This completes the contribution of this thesis towards a multithreaded, multi-core, network-level energy model for an embedded real time processor.

A broader view is applied in Chapter 10, which looks beyond the XS1 processor to identify how the contributions made in this work could be applied to other architectures. Several architectures are surveyed, indicating where common characteristics may be present, and where novel features may require new research in order to further the state of the art in energy modelling of software.

Finally, the thesis is concluded in Chapter 11. The chapter contains a review of the contributions made, a summary of all evaluations made throughout the work, and a description of future work opportunities that have either been discovered during this research, or created as a result of it.

## 1.4. Terminology and conventions

A small summary of critical terminology and chosen conventions are described herein. Other terms are defined as necessary throughout the document. Acronyms are expanded upon the first instance of their use and also in the List of Acronyms (LoA).

#### Power and energy

In this thesis the terms power and energy are used frequently. These terms are often interchanged in literature, but in the context of this work it would not be appropriate. For clarity, therefore, their definitions are given.

Power, P, or power dissipation, is an instantaneous measure of a rate of energy transfer, or the rate at which work is done. It is quantified in Watts, or W. Energy, E, or energy consumption, is a measure of total work done. This is the amount of charge that traverses the potential difference present in a circuit. This process transforms the energy, mostly from electrical form into thermal form. The charge present in the system is not constant, nor necessarily are the potential differences. As a result, power changes continuously. Energy therefore is the integral of power during a period of time, per Eq. (1.1). It is typically expressed in Joules, or J.

$$E = \int_0^T P(t)dt \tag{1.1}$$

Applying both the concepts of energy and power, a system that sustains a constant power dissipation of 1 Watt for 1 second, will have transferred 1 Joule of energy.

#### Multi-threaded and multi-core

A number of the processors in this work require a distinction between *multi-core* and *multi-threaded* to be made. This culminates in the study of a system that has both of these properties. The term Multi-Threaded and Multi-Core (MTMC) is used to refer specifically to this type of system. For further clarification of the distinctions, parallelism's various forms in both software and hardware are detailed in Chapter 2.

Part I.

Background

## Introduction

Part I of the thesis introduces the research and components that form the foundations of the contributions presented in Part II. There are three essential topics: parallelism, energy modelling and energy saving. These are each covered in turn, with the inclusion of the referenced research justified in relation to the goals of this thesis.

The final chapter in this part introduces the hardware platforms upon which the majority of this thesis bases its work. This chapter includes the work that was put into developing the Swallow system in a platform that was usable for the profiling, analysis and modelling presented in Part II.

## 2. Parallelism and concurrency in programs and processors

This chapter provides a review of the technology and concepts behind parallelism and concurrency in hardware and software. It starts with programming and multi-tasking concepts in § 2.1, then examining single-core parallelism in § 2.2 before reviewing multi-core technologies that are becoming increasingly prevalent in modern computing in § 2.3. Where appropriate, the literature is reviewed in the context of embedded systems, although a broader view is suitable for much of this chapter.

The distinction between parallelism and concurrency is important to the understanding of MTMC systems and how to express programs for them. *Concurrency* allows components to make progress independently of each other, such that in a given period of time, all of the components can have performed work. However, this can be achieved by sub-dividing the observed time period, allocating a division of that time to each component, so that at any given point in time, only one component is doing work. *Parallelism* provides simultaneous progression of components, therefore multiple activities can happen at the same time.

The notion of parallelism is present throughout the history of computing, with Flynn establishing a taxonomy of computer architectures that remains relevant today [Fly72]. From this taxonomy, both Single Instruction Multiple Data (SIMD) and Multiple Instruction Multiple Data (MIMD) require parallelism of some kind, both of which are relevant to this thesis. In addition, Single Instruction Single Data (SISD) implementations can also contain some degree of parallelism when sequences of SISD instructions are considered. These are all explored in this chapter.

In the software domain, programs may express solutions to problems in ways that are concurrent. These are activities that *can* take place at the same time, conceptually. The execution of these programs may be serialised and therefore not parallel, whilst still retaining the property of concurrency [AS83, p. 4].

Parallelism and concurrency exist across the hardware/software stack, from programming paradigms that aid the expression of concurrent problems [Pin98], techniques to parallelize sequential non-dependent operations, through to the necessity to parallelize hardware, brought about by technological limitations [Kah13].

## 2.1. Concurrent programs and tasks

There are numerous forms of concurrency exposed at the software and programming levels. Concurrency can allow multiple independent workloads to be processed simultaneously if support for parallelism is present in the system (§ 2.1.1). Alternatively, a single problem, when written appropriately, can be expressed as a concurrent program (§ 2.1.3). When communication or response to events is required, techniques to handle multiple events in a desirable order and with adequate responsiveness must be used (§ 2.1.4). All of these rely on multi-threading either in expressiveness or implementation. This section begins with an overview of multi-threading and several related terms.

## 2.1.1. Multi-threading

Multi-threading is common across all computing, from high-performance scientific computing, through general purpose and down to embedded computing. The basic principle is to express multiple activities that may take place concurrently. There is a distinction between a multi-threaded view of a system, and how those threads are actually executed by the underlying processor(s). Many of the implementation details at the hardware level are discussed in the subsequent sections of this chapter. However, in this section, the software and Operating System (OS) level are the focus.

Depending on the context of the system, threads might also be termed tasks or processes. The distinction between them, if one exists, may differ. For example, in the Linux kernel [Mcc02], which closely follows the Portable Operating System Interface (POSIX) threading standards, a *process* is an address space and set of resources dedicated to the execution of a program, while a *thread* is an independent path of execution within a process; there may be one or more threads in a process. A *task* is a basic unit of work in Linux. If a process is cloned and some resources shared between instances of that process, then a set of cooperating tasks is created.

#### Defining multi-threading

For the purposes of this thesis and in the context of embedded systems, where an OS or POSIX implementation may not always be used, the term *process* is avoided except where supporting literature uses it. Terms relating to *threads* and *tasks* are defined as follows:

- **Software thread** A unit of sequential execution, which may form the entirety of a program, or may work alongside other threads to achieve a common goal. This provides concurrency.

- **Hardware thread** A front-end to a processor retaining its own program counter and other registers, able to accommodate a software thread. The computational resources behind the front-end may be shared, allowing multiple threads on a single processor core. This provides parallelism.

- **Task** A separation of units of work that may have constraints such as hard real-time deadlines. A set of tasks might be realised as a group of time-sliced software threads managed by a Real-Time Operating System (RTOS), or they might be allocated as separate hardware threads on a sufficiently capable system. In any case, some tasks may need to complete their activities within a given time period.

### 2.1.2. Parallel tasks

An embedded system may have multiple objectives to achieve, defining multiple tasks. For example, take an embedded real-time system which is responsible for controlling an industrial process. It may have multiple sensors to communicate with, each of which requires data processing, along with actuators that must be controlled based on the result of that processing. It may also need to provide interfaces for reconfiguring the parameters that direct the processing of sensor data or control of actuators. Several interfaces will be involved in such a system, possibly implementing a range of protocols, such as Inter-Integrated Circuit (I<sup>2</sup>C), Ethernet and Controller Area Network (CAN).

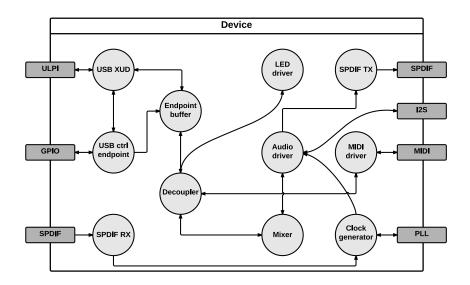

Figure 2.1 depicts a USB audio application for an XMOS-based platform [XMO14a]. It comprises several inter-connected tasks. There are tasks for I/O over various interfaces, as well as audio processing. The I/O protocols each have timing requirements, defined by the standards and behaviour of the components that are using them. As such, the embedded system must be able to send and receive data to and from these interfaces within their specifications. Further, for the system to operate correctly, there may be additional timing constraints that need to be applied. For example, in the context of an audio application, delayed audio processing could result in undesirable latency, or audible glitches caused by lost samples.

In such a system, all of these tasks must be able to run with sufficient speed and frequency in order to meet the timing requirements. In some implementations, an RTOS may be used to help with allocation of resources to meet these requirements. There may still be a need for the system software developer to correctly define priorities.

In general purpose computing, the OS also has task scheduling responsibilities, although the majority of tasks, particularly those initiated by users, are not considered time critical or only have soft deadlines (a missed deadline is inconvenient rather than system-breaking). Different scheduling techniques are used depending on the OS used and how it is configured. For example Linux and Windows have different schedulers and scheduling options [BC05; Mic12].

Figure 2.1: A multi-threaded task structure in a USB audio application.

## 2.1.3. Parallel programs

Certain types of programming problems, such as multi-stage processing, client-server and data parallelism, can be implemented in single programs that contain some level of parallelism. They can be distinguished from parallel tasks in that they cannot be separated from the other parts of the program and remain useful, or they are simply a replicated component. For example, an Ethernet interface task might be modularised to be used in multiple applications. A concurrent matrix multiplication algorithm, however, may replicate worker threads that each process a subset of the input data.

Software such as pigz [Adl10] allows data compression to be performed concurrently and is designed to exploit available parallelism in a system. The POSIX threading system is used for OS portability in pigz. The sc\_matrix library, used in Chapter 7, expresses a number of vector and matrix operations concurrently, although it is targeted at bare-metal embedded programs rather than at devices running an OS and so exploits device specific parallelism features rather than a portable threading library.

Client-server arrangements can often exploit parallelism, in that a server may need to handle multiple clients simultaneously. The widely used Apache web server can use multiple worker threads or processes to serve a larger number of client connections simultaneously. The performance of such an implementation is both workload and configuration dependent, making it an area of interest to research in web technology [DKC08].

Many libraries and languages have been created to allow parallelism to be expressed in programs. Open Multi-Processing (OpenMP) [DM98] is a library that provides extensions to Fortran, C and C++ to enable shared-memory programming. The Message Passing Interface (MPI) standard [Sni98] provides methods for communicating between threads in parallel systems. Open Compute Language (OpenCL) [SGS10] provides a language and framework for leveraging parallelism in heterogeneous systems, allowing work to be allocated to different compute units, such as Central Processing Units (CPUs), Graphics Processing Units (GPUs) and Field Programmable Gate Arrays (FPGAs) [Cza+12]. There are many more languages, each expressing parallelism using different paradigms [Pin98], including Occam, MultiLisp, and Sire [Han14]. Message passing is a commonly used abstraction for parallel programing, two notable forms are formalised as Communicating Sequential Processes (CSP) [Hoa78] and the Actor model [Kow88]. The former uses communication channel ends with synchronisation, whilst the latter uses mailboxes at the receiver. The communication model of the XS1 architecture, described in Chapter 5, follows a CSP model of parallel processing. Other methods of communicating in process networks exist, either synchronous or asynchronous in nature [Mar11, pp. 21–118]. The choices for expressing parallelism in programs is rich and varied. To some extent, choices are driven by particular application areas. In the embedded space, a significant proportion of applications continue to be developed in C or its derivatives [Phi04, p. 151]. Although alternatives exist [Taf14], the inertia present from a significant amount of historic code, means that C is likely to remain a popular choice for the foreseeable future.

### 2.1.4. Event driven software

In event driven software, waiting on the availability of data, for example through I/O, is kept efficient by avoiding activities such as spin locks. Examples of this and alternative constructs are given later, in § 4.4. Event driven behaviours allow applications to wait without wasting CPU cycles, and for inputs to be queued for handling with minimal blocking. Event handling is an activity often handled by the OS, the software interfaces to which vary between OSs. Libraries such as **libevent** [Mat10] provide an abstraction layer on top of these various implementations. Languages that provide channel or other communication based abstractions must also rely on event implementations at a lower level in order to efficiently provide their data sharing model.

Software such as the nginx [Sys14] web server use events to handle the so-called C10k problem, where ten thousand client connections may need to be maintained simultaneously. Although the processing of this number of connections may not be fully parallel, the software architecture is able to accommodate this many open connections with low overhead.

In embedded computing, interrupts are frequently used to avoid polling of devices that may or may not be ready for some activity to be performed upon them (for example, a device buffer may be free to receive more data). Interrupts exist in both a hardware and software sense. A *hardware interrupt* uses an I/O signal to cause a context-switch in the processor that receives the signal. Typically, an Interrupt Service Routine (ISR) is entered, which deals with the cause of the interrupt, before returning to the previous context. Interrupts may be masked to avoid context switching in time-critical sections of software, and interrupts may also be nested or prioritised, so that multiple simultaneous interrupts, from numerous sources, can be handled appropriately.

If there is no computation to be performed, interrupts can be exploited for power saving. An idle processor can sit in a low power or sleep state until an interrupt triggers a wake-up into its fully active state. Thus, interrupts can be used not just for rapid context switching, but also power state transitioning. For example, many ARM devices feature *wait-for-interrupt* instructions that put the device into low power mode until an interrupt takes place. Similarly, the XMOS XS1-L can do this with both conditional and unconditional wait instructions.

A software interrupt uses a similar context-switch approach, but the activity is handled, and possibly initiated by an OS. For example, the OS may interrupt a running program to allow another to have processor time, thus achieving time-slicing multi-tasking. Alternatively, a program may cause a software interrupt in order to request a privileged activity from the OS, such as disk access.

Interrupts create scheduling challenges and potential context-switch overheads [Tsa07; TT09]. Certain multi-threaded architectures, such as XS1, also implement *events*. These are similar in behaviour to interrupts, except context is not preserved when an event takes place; the thread responding to the event simply jumps to a designated program location. This allows a thread to efficiently wait to respond to one of multiple possible events, whilst other threads continue to execute. The hardware architecture and distribution of work between threads then become the determining factors in responsiveness, rather than context switch and ISR overheads. The XS1 event handling implementation is discussed in more detail in Chapter 5.

## 2.1.5. Summary

This section has provided background on various parallel processing and concurrent programming paradigms, technologies and challenges. A number of these are relevant across computing while others are more specific to embedded systems or at the OS level.

In task concurrency, a program may comprise multiple threads, all working on independent tasks, with communication where necessary. Libraries such as POSIX threads, or a RTOS provide a means of defining these tasks.

| Cycle | Stage 1 | Stage 2 | Stage 3 | Stage 4 | Stage 5 |

|-------|---------|---------|---------|---------|---------|

| 0     | IO      |         |         | _       |         |

| 1     | I1      | IO      |         | _       |         |

| 2     | I2      | I1      | IO      | _       |         |

| 3     |         | I2      | I1      | IO      |         |

| 4     | I3      | _       | I2      | I1      | IO      |

| 5     | I4      | I3      |         | I2      | I1      |

Table 2.1: Example of a five stage processor pipeline including warm-up and stalling.

In a single concurrent program, inseparable tasks are composed together, with an expectation that each task can progress at any given time (save for synchronisation and communication). Programming languages such as Occam and Sire allow concurrency to be expressed in algorithms. This concurrency can then be used to realise parallelism on a suitably equipped hardware platform.

At the hardware and low level of software, interrupts and events allow asynchronous activities to be handled concurrently. There is motivation to minimise the overhead of handling these, both to ensure correct operation thus avoiding missed deadlines, and to provide good scaling, serving ongoing application challenges such as C10K.

The next two sections discuss how parallelism is made possible in hardware. Thus, the concurrency presented by the various techniques in this section have the potential to be exploited as parallelism by the underlying computer architecture.

## 2.2. Parallelism in a single core

At the hardware level, there are two main approaches to maximise performance. The first, is to increase the operating frequency of the processor, so that a newer, faster processor can deliver a higher throughput of work in a given unit of time. The second, is to do more work per clock cycle, such that a new processor with a higher Instructions Per Clock (IPC) can do more work in a given unit of time, at the same frequency.

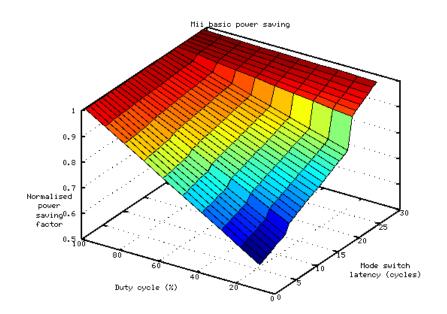

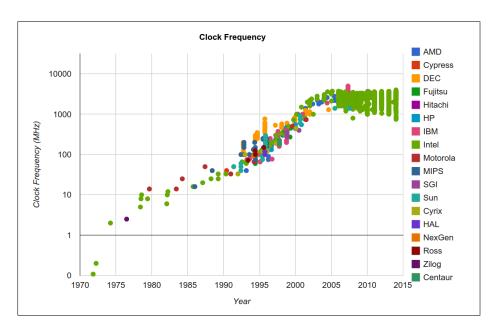

The former has been maintained through lower threshold and operating voltages combined with increased transistor count at the same power density, per Dennard's scaling observations [DGY74]. However, at 130 nm feature size, this property has ceased to hold [Kuh09; Boh07]. This has resulted in a plateau in processor operating frequency since 2005 [Kah13]. To maintain competitiveness, processor manufacturers have sought and continue to seek methods for maximising IPC and throughput, creating parallelism of various forms in a single core.

If the objective of higher performance is substituted for lower energy, then a processor that can do more work per clock cycle than another can be run more slowly, and potentially at a lower voltage, whilst maintaining performance. In these conditions, it will most likely be the more energy efficient processor of the two.

This section examines methods of increasing IPC and throughput, all of which have an impact not just on performance, but on energy consumption and how such processors can be modelled for energy, as will be discussed in Chapters 3 and 4.

## 2.2.1. Pipelining

The majority of computer architectures break execution of instructions down into multiple stages, forming a pipeline. A sequence of instructions can be processed in this pipeline, progressing between stages on each clock cycle. For an N stage pipeline, up to N instructions can be executed simultaneously. The execution latency of an individual instruction is not improved by pipelining. However, the next instruction can begin to be processed before the current one is completed, thus increasing throughput. In addition to this, smaller stages typically allow a higher operating frequency for the processor, by shortening the critical path.

An example of instruction occupancy of a pipeline is given in Table 2.1. In ideal circumstances, the pipeline is always full. At the start of execution, the pipeline must *warm up*. Further, instructions may need to wait for an earlier instruction to complete before proceeding. For example, two

| Start    | Decode                    | Issue I0, I2      | Issue I1 & I3,<br>complete I0, hold I2 | I0-2 completed |

|----------|---------------------------|-------------------|----------------------------------------|----------------|

| Decoder  | I3<br>I2 I1 I0<br>Decoder | Decoder           | Decoder                                | Decoder        |

| FU FU FU | FU FU FU                  | 10 12<br>FU FU FU | FU FU FU                               | FU FU FU       |

| ROB      | ROB                       | ROB               | ROB<br>10                              | ROB            |

Figure 2.2: An abstract example of instruction flow through a super-scalar processor.

consecutive instructions may use the result of the previous instruction as a source operand. If the previous instruction is not completed before the current instruction proceeds, the wrong operand value would be used. This is a *data hazard* which must be detected and avoided, either by *stalling* the pipeline (shown at cycle 3 in the table), which reduces IPC, or adding forwarding logic into the pipeline [Pat85, pp. 17–19], increasing pipeline complexity.

Another example is branching, where a decision to branch may invalidate instructions that have already entered the pipeline. This requires the pipeline to be *flushed* (emptied), again reducing IPC. As the depth of a pipeline increases, the performance penalty from a flush increases. Branch prediction techniques [Smi81] or branch delays [Pat85, pp. 12–13] can be used to try to avoid this scenario.

### 2.2.2. Super-scalar

Where a processor possesses multiple Functional Units (FUs), such as Arithmetic Logic Unit (ALU), Floating Point Unit (FPU) and memory unit, IPC can be increased by attempting to utilise as many of these in parallel as possible. If one unit is in use and requires multiple cycles to complete, it may be possible to issue an instruction to another unit, provided there are no data hazards between instructions. These *super-scalar* designs allow multiple instructions to be executed simultaneously [Joh89]. Throughput can be improved further by allowing out of order execution, where instructions are issued internally in an order that maximises FU utilisation whilst avoiding data hazards, with re-ordering hardware at the end of the pipeline [HP06, pp. 104–114], so that instructions are seen externally to complete in the order that was expressed within the software thread.

An abstract view of a super-scalar processor is shown in Figure 2.2, capturing the progression of several sequential instructions at various points in time. The diagram shows several techniques that contribute to Instruction Level Parallelism (ILP) in a super-scalar system, including pipelining, sub-pipelining, multiple instruction issue and re-ordering. Initially, two of the instructions can be issued to different FUs, but a third cannot as the target FU is already in use. This results in instruction I2 overtaking I1, so it must be held in the Re-Order Buffer (ROB). Once I1 completes, the ROB can retire both I1 and I2. I3 is still executing at this point, because the sub-pipeline of the FU that it is utilising takes a larger number of cycles than some other FUs.

#### 2.2.3. Hardware threads

Introducing hardware threads to a processor core allows further exploitation of the previously described methods by fetching multiple sequences of instructions that can be fed into the pipeline and FUs. The presence of multiple hardware threads provides the benefit of avoiding data hazards between instructions by having more than one context to choose from.

Hardware multi-threading requires multiple register banks, one for each thread, along with additional logic to fetch and buffer instructions from multiple memory locations. Further, there may be some replication in the instruction decode logic. This adds to processor complexity.

In ideal operation, multiple threads can be used to keep all FUs and pipeline stages full, to the benefit of IPC. However, it is also possible that threads may contend the same FUs, leading to similar performance to a single-threaded processor. At an OS level, the scheduler may need to be aware how a processor's multi-threading is implemented, as the OS may otherwise treat it as an independent processor core, assuming that resources on that core are uncontested.

An example of multi-threading can be found in Intel's Hyper-Threading [Int03a] technology, which provides two front-ends to a single super-scalar core and has been used in a variety of Intel processors including the Pentium 4, Xeon, Atom and Core product ranges. Other processors implement multiple cores each with multiple front-ends, such as the Sun Sparc 32-way Niagara processor [KAO05], which comprises eight cores each with four-way multi-threading. The AMD Bulldozer micro-architecture implements two threads per core, but with a shared FPU and two integer pipelines [But+11]. This created an example of the aforementioned OS scheduling issues, which needed to be resolved to ensure best performance, for example in the Windows 7 OS [Shi12]. The XMOS XS1 processor [May09b], which is described in detail in § 5.1, provides eight hardware threads, sharing a simple four-stage pipeline, in which IPC is only maximised when four or more threads are active.

#### 2.2.4. Data parallelism

The previously described techniques all apply to SISD structures. However, SIMD can be exploited in a single processor core for certain data maniuplation tasks. Various ISAs contain extensions that provide SIMD instructions and registers. For example, ARM NEON [ARM14] and Intel Streaming SIMD Extensions (SSE) [RPK00] can perform instructions upon wide vectors of data up to 128 bits. Intel Advanced Vector Extensions (AVX) [Lom11] can operate on 256-bit wide data sets.

GPUs, in particular those with General Purpose GPU (GP-GPU) capabilities can handle a large amount of data parallelism per core. Such devices, while present in some high performance embedded devices, like mobile phones, do not fall within the area of research explored in this thesis.

Very Long Instruction Word (VLIW) processors conform to a MIMD organisation, where multiple operations are performed on a set of data in a single instruction. Such technology is most frequently used in embedded Digital Signal Processors (DSPs) [FDF98], where software-pipelined activities can be expressed as a series of VLIW sub-instructions. VLIW processors perform MIMD in lock-step, where the long instruction encodes the various operations that will be performed on each operand. Therefore, in VLIW processors, the compiler must be able to schedule instructions in order to maximise IPC and satisfy data dependences, otherwise hand-optimisation may be required to attempt to perform useful operations in the slots available in the instruction encoding.

## 2.3. Multi-core processing

Multi-core processors provide several independent processing units, with no contention for the resources on each core, forming a MIMD organisation. This forms the distinction between these and multi-threaded processors, where a multi-threaded processor creates the possibility to execute more than one instruction sequence simultaneously, but shares FUs internally and may not necessarily have MIMD characteristics. However, contention of resources is not completely removed by multi-core architectures. The memory hierarchy and interconnection between cores can still be contended and indeed this forms a significant problem in achieving good performance in multi-core systems. This is particularly significant if it is not possible to scale the interconnect with the rest of the

system, which is another observation of Dennard [DGY74] that is problematic in modern processor design [Boh07].

A multi-core processor has more than one core on a single die or chip, distinguishing it from a multi-processor system in structure. Ultimately a system comprising a large number of cores may be formed of multiple processors, each with multiple cores, and each capable of multi-threading. Indeed, this is the case for the Swallow system described in Chapter 8 as well as many server systems. For simplicity, this thesis refers to systems of multiple multi-threading capable cores as MTMC, distinguishing between chip-local multi-core and system level multi-processing only where necessary.

A wider view of the different types of multi-process architectures, predominantly from a general purpose computing and server perspective, is given by Roberts and Akhter [RA06, pp. 5–13].

## 2.3.1. General purpose multi-core

The first general purpose x86 multi-core processors were introduced in 2005, with both AMD and Intel offering dual-core products. The number of cores has since expanded, with currently announced products containing as many as 18 cores, for example the Intel Xeon E5-2699V3. Many ARM-based products are also multi-core, including a number of Cortex-A series devices, commonly found on mobile phones, but also in servers and high performance embedded multimedia devices.

Multi-core is reasonably well suited to general purpose computing, where even a single-user machine is frequently used for multiple concurrent tasks. These may include user-triggered activities, such as multimedia, web-browsing and gaming, but also compute-intensive background tasks, such as virus scanning and data indexing. However, there is still sufficient demand for single-threaded performance, that multi-core processors may offer aggressive Dynamic Voltage and Frequency Scaling (DVFS) strategies that provide temporary boosts to core frequency and voltage when a single thread will benefit. Intel's Turbo Boost [Int15] is an example of this. Such techniques are typically only temporary performance boosts because the power demand would push the processor beyond its Thermal Design Power (TDP) with prolonged use and sustained operation at this higher frequency/voltage would likely have a negative impact on device longevity and reliability.

### 2.3.2. Embedded multi-core

Multi-core processors in the embedded space include various designs, often targeting communication or other hard real-time environments. Companies including Picochip, EZChip, XMOS and Adapteva have developed architectures that directly serve embedded use.

The Picochip PicoArray processor [DPT03], contains an array of signal processing cells on a Time Division Multiplexing (TDM) network, principally for implementing cellular communication modems and codecs. The Adapteva Epiphany and EZChip Tile processors are described in more detail in Chapter 10, forming part of this thesis' discussion of modelling a wider range of multi-core devices.